# THE ELECTRONICS RESURGENCE INITIATIVE

**OPENROAD:** FOUNDATIONS AND REALIZATION OF OPEN, ACCESSIBLE DESIGN

.....

.....

# ANDREW B. KAHNG

#### **UC SAN DIEGO**

#### THE DESIGN CHALLENGE

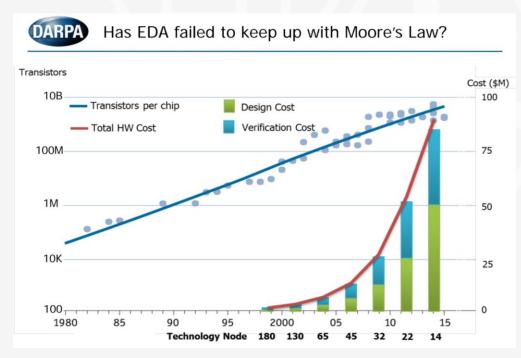

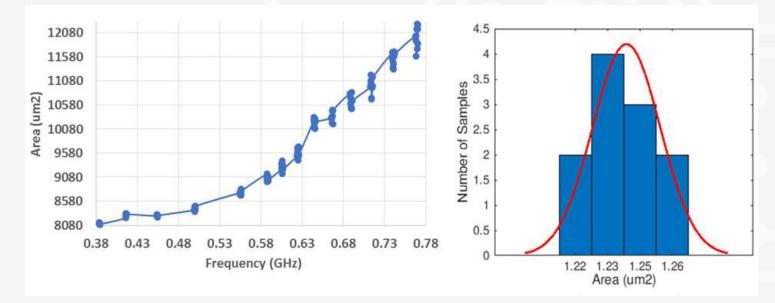

• Enormous barriers to hardware design in advanced technologies: Cost, Expertise, Unpredictability

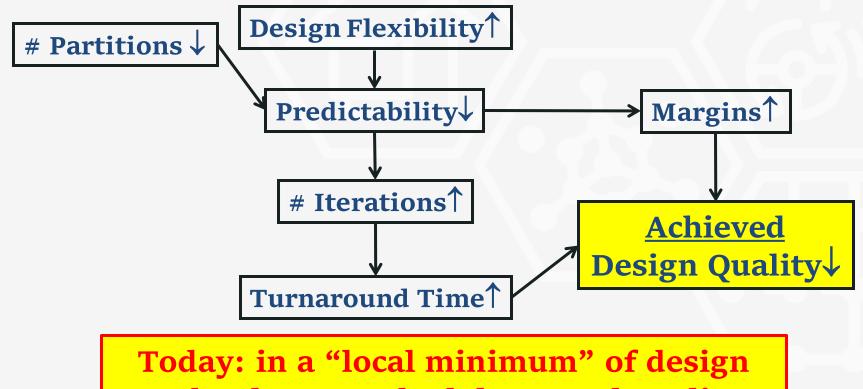

#### **HOW IS IT DONE TODAY?**

- Hardware design tools have evolved into complex "Swiss army knives"

- Chaos when tools are forced to "try hard"

#### **"LOCAL MINIMUM" OF HW DESIGN**

technology, methodology, and quality

#### **NEW IN OUR APPROACH**

#### 24 hours, no humans – no PPA loss

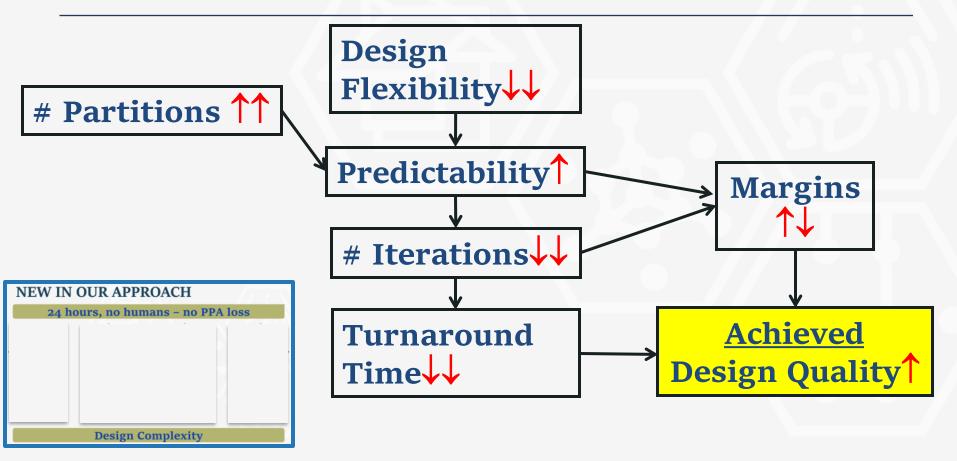

### FOUNDATIONS OF OUR APPROACH

- No Humans: tools must adapt and self-tune, must never get stuck unexpectedly

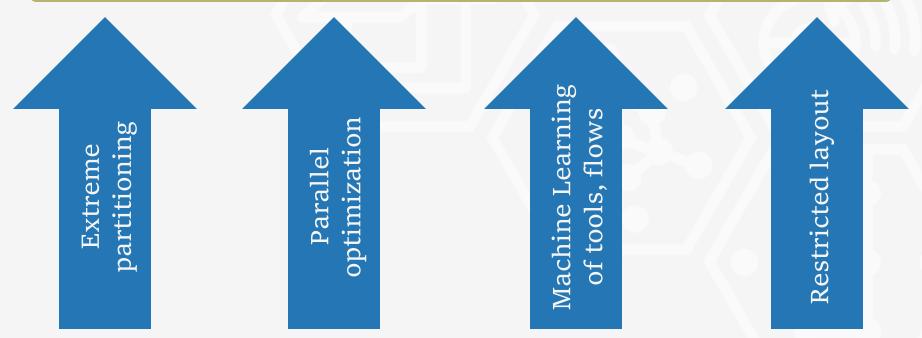

- 24 hours: extreme partitioning of problems

+ parallel search on cloud

+ machine learning for predictability

- Mantra: Correctness and safety by construction

- Mantra: Embrace freedom from choice

#### **A NEW DESIGN PARADIGM**

#### **TECHNICAL CHALLENGES**

- Data: small and expensive!

- Humans: are in the loop for good reasons!

- Fundamental tradeoffs: analysis cost vs. accuracy, optimization effort vs. quality

- Activation energies: new sharing mindsets, open-source ecosystem

### **OUR GOAL**

- 24-hour, No-Human-In-Loop layout design for SOC, Package and PCB with no Power-Performance-Area (PPA) loss

- Tapeout-capable tools in source code form, with permissive licensing  $\rightarrow$  seed future "Linux of EDA"

### **IMPACT IF SUCCESSFUL**

- Create new "Base Technologies" that enable 24-hour, **autonomous** design

- Extreme partitioning (bite-sized problems)

- Parallel search and optimization

- Machine learning: models of tools, designs

- New paradigm for design tools and methods: autonomy first

- Bring down barriers  $\rightarrow$  democratize HW design

### **IMPACT ON DESIGN COST**

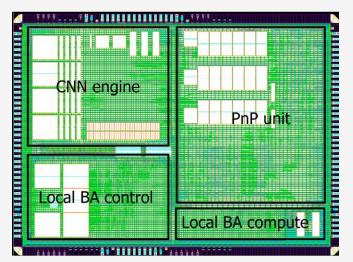

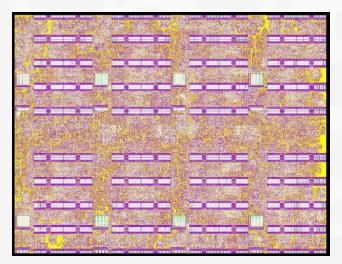

- Embedded vision chips (28nm/16nm) from Michigan Internal Design Advisors team

- Layout @Michigan: 10+ weeks, significant resource

- OpenROAD and IDEA goal: 1 day, no humans (!)

## **SWINGING FOR THE FENCES**

Must achieve critical mass <u>and</u> critical quality

#### 11 of 13 IDEA TA-1 subtasks

+ Base Technologies, Design

| Common           | Databases / Processing |                            |

|------------------|------------------------|----------------------------|

| Infrastructure 🗸 | Cloud Infrastructure   | BROWN                      |

| ✓                | Timing Analysis        | <b>₹</b><br>UCSD           |

| ✓                | Parasitic Extraction   | UNIVERSITY<br>OF MINNESOTA |

| ~                | Readers + Writers      | (III)                      |

| ~                | Power and SI Analysis  | UNIVERSITY<br>OF MINNESOTA |

| Layout 🗸         | Logic Synthesis        | BROWN                      |

| Generators       | Floorplanning          | ILLINOIS                   |

| ✓                | Placement              |                            |

| ✓                | Clock Tree Synthesis   | ₹<br>UCSD                  |

| ~                | Detailed Routing       |                            |

| ~                | Layout Finishing       |                            |

| Design           | SoC-Design-Advisors    | 0000                       |

## **SWINGING FOR THE FENCES**

- Internal Design team (Michigan)

~70 Ph.D., 50 M.S. graduates

+ 15 new SOC designs each year

- Tools team (UCSD, Illinois, UMinn, UT-Dallas, Brown):

~150 Ph.D., 80 M.S. graduates

+ many tools, engines "on the shelf"

- Qualcomm: HW design, SOC-Pkg-PCB

- Arm: IP, system design + ML guidance

### AND MORE ...

- Open-sourcing of commercial timing engine

- Donated commercial tool source code base

- Industry advisors and technical contributors

- Dr. Chi-Ping Hsu, Avatar

- Dr. Noel Menezes, Intel

- Dr. Richard Ho, Google

• Worldwide outreach, engagement, support ...

#### **ERI** ELECTRONICS RESURGENCE INITIATIVE

#### S U M M I T

#### 2018 | SAN FRANCISCO, CA | JULY 23-25