Professor Erick Carvajal teaches VLSI and microelectronics based courses at the University of Costa Rica. In 2021, he was actively looking to set up his undergraduate, Microelectronics course using conventional EDA tools. However, these were very expensive and difficult to set up for the class requirements given software licensing constraints and server resources limitations. Hence he started looking for other alternatives– he learned about OpenROAD™ through a Google sponsored presentation in 2021.

His goals were to provide easy-to-use and access EDA tools and course content to enable his students to learn basic IC design concepts and flows, both collectively and independently, within a semester. Most importantly, he wanted the flexibility to tailor the course for his Spanish students who did not have any other source of learning material. Erick also wanted to ensure that his students have a viable path to employment in the semiconductor Industry beyond the opportunities in Costa Rica. Hence he chose OpenROAD as the OpenEDA application of choice for his course that is ideal particularly for regionally underserved communities.

The usage of OpenROAD™ as a key OpenEDA source for VLSI education and curriculum for workforce development is rapidly growing since it provides easy, scalable and open access to the entire tool suite, flow control options and design cases on multiple technology platforms. This story features the exemplary work of Erick and his students who resourcefully took advantage of OpenROAD in this new era of open source based learning and in semiconductors.

OpenROAD actively engages with motivated Universities and researchers worldwide to provide training and curriculum support as part of its vision to democratize and spread the learning of VLSI and enable a path to skilled workforce development.

Course – Key Flow concepts with Hands-on learning

The semester-long course, from August-December, covered the entire IC design flow RTL-GDSII flow with key VLSI design and open PDKS using OpenLane, the flow controller by Efabless, based on OpenROAD™ , and Skywater 130nm. The course duration was a total of 16 weeks with 4 hrs/week allocated to lectures and lab discussions. Students completed labs online as homework. The prerequisite for this course was basic semiconductor devices knowledge as covered in the seminal textbook CMOS VLSI DESIGN: A Circuits and Systems Perspective By N. Weste and D. Harris

The course included three labs aimed at providing students with a depth of training on core concepts of the RTL-GDSII design flow using OpenLane. One such design example was a basic 8-bit adder.

Open Source learning offers limitless potential for creativity.

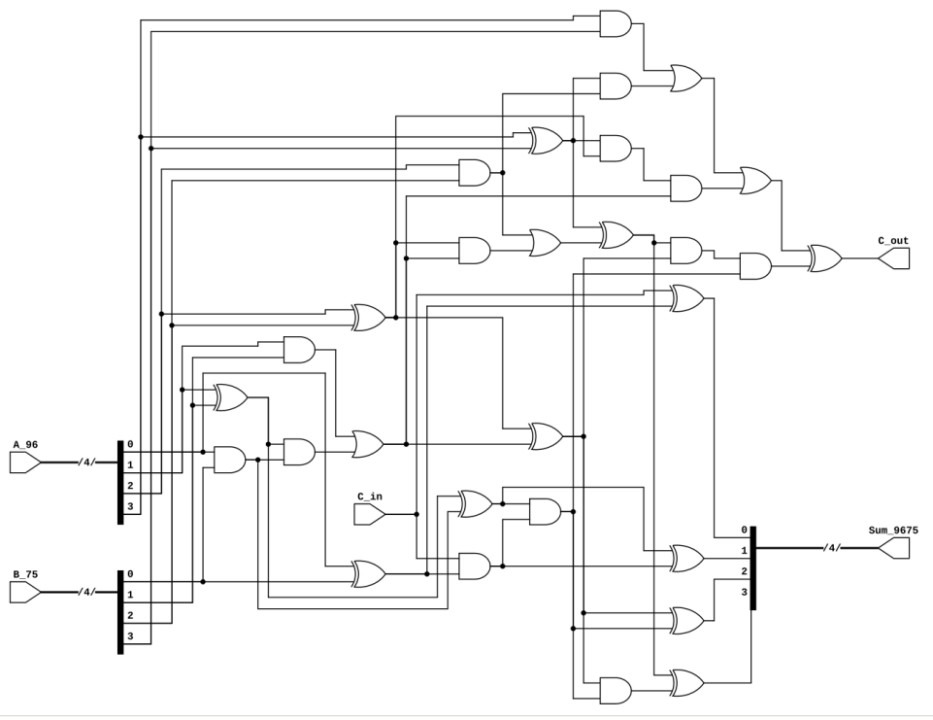

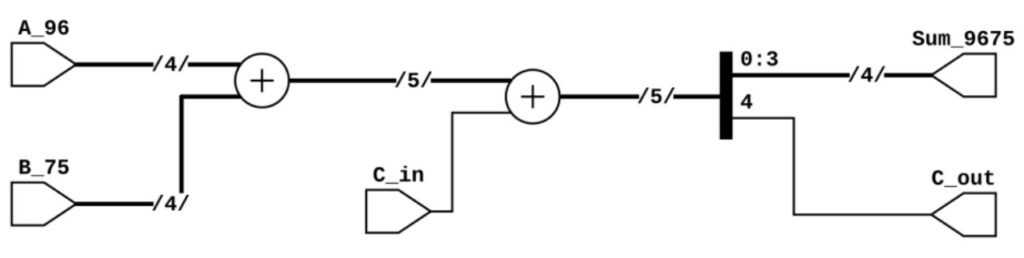

The current OpenLane flow does not contain a RTL schematic viewer. The team found a useful way to visualize the Yosys synthesized netlist using netlistsvg: (https://github.com/nturley/netlistsvg). This allowed students to view the netlist as a schematic for design exploration and specially to understand technology mapping visually. This tool takes a netlist in a JSON format (which can be generated in Yosys using the write_json command) and outputs an SVG image of the circuit. Figure below shows a 4 bit adder. The values on the signals (e.g. A_96, B_75) were personal identifiers assigned to each student to validate their individual work.

Diagram before technology mapping *

*A bug in netlistsvg renders the two output port directions incorrectly as inputs

Diagram after technology mapping *

*A bug in netlistsvg renders the two output port directions incorrectly as inputs

Design Exploration enables PPA comparisons

In the labs, students explored multiple synthesis strategies and design configurations based on changes to pin configurations, floor plan aspect ratios and various power grids for a fixed die size.

Students learned to experiment, analyze design choices and arrive at the best possible PPA results i.e area and the critical path delay based on comparisons to generated layout–all of which they could do so very rapidly in a matter of just a few hours. The OpenROAD™ GUI based detail analysis and visualization features allowed them to study the impact of design changes at various flow stages and thereby converge to the final layout.

GUI based Visualization for easy analysis and feedback

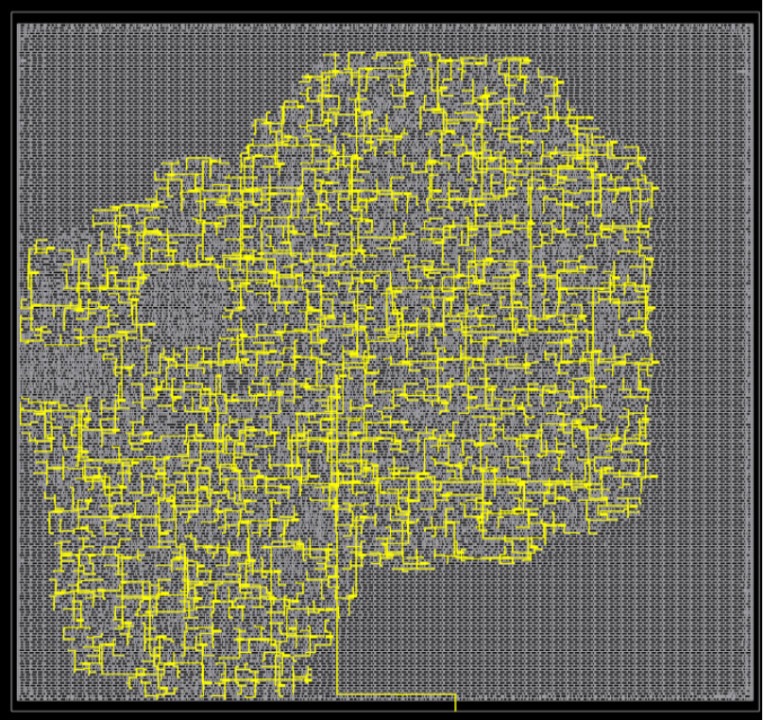

Here’s an example of a clock tree generated for a Huffman JPEG encoder displayed in the OpenROAD™ GUI: https://github.com/The-OpenROAD-Project/OpenLane/blob/master/designs/y_huff/src/y_huff.v

Clock Tree for a Huffman JPEG encoder

Macro Placement Exploration

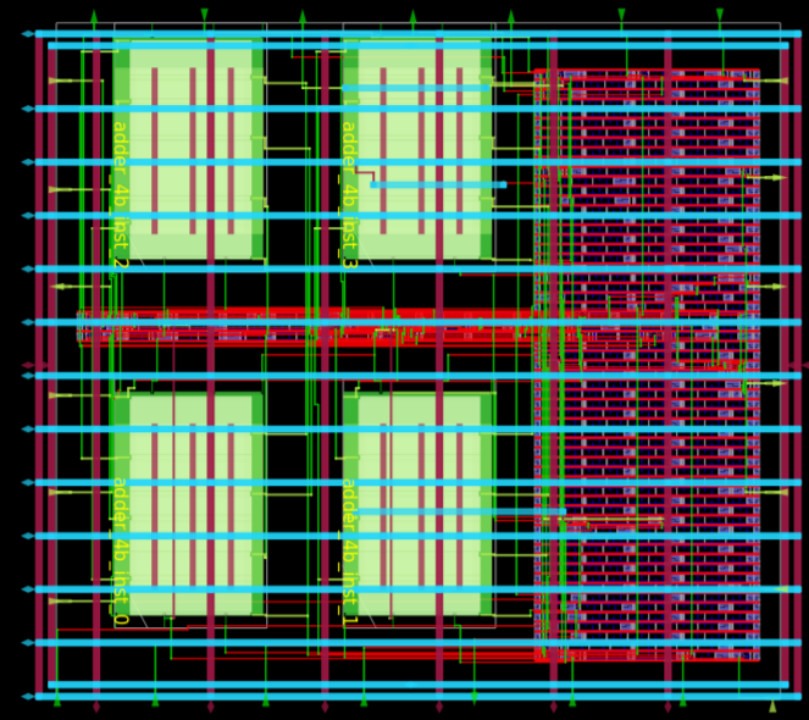

Students also learned how to create a macro and then instantiate multiple instances at the top-level. Here’s an example- Macro for 4 bit adder first created at block-level and then instantiated in an 8 bit ALU. Students played with pin positions of macros and top level, as well as various cases for good macro placement.

Sample Layout created by students for the 8 bit ALU with macros

What’s Next?

Prof Erick Carvajal plans to offer a full semester based on an OpenROAD™ based capstone project in addition to the current course. He is also eager to collaborate and share his work with other Spanish learners. Interested users can reach out to him directly via his email: erick.carvajalbarboza@ucr.ac.cr. Course materials will be made available sometime in January 2023. So stay tuned for updates.

Here’s a summary of his experience in his own words about how OpenROAD is a powerful aid to Open Source learning and contribution.

“OpenROAD™ was essential for the class I taught. The OpenLane based flow was easy to set up, so the students were not stuck at unnecessary steps, and the ramp-up was very fast. Students were able to learn and gain practical experience with EDA tools: analyze reports, debug errors, optimize the design, and have a free and safe environment for experimentation and exploration. The concepts we covered have already helped some of the students to get good jobs at physical design roles in big companies, and sparked the curiosity for VLSI in others, who are already trying to get involved in bigger projects using OpenROAD. One of my students already working in the industry expressed to me that he was able to gain a better understanding of the tasks he was performing at his job. OpenROAD is, without a doubt, democratizing VLSI education and spurring research opportunities–it gave me the chance to teach a class I couldn’t afford.”

About Professor Erick Carvajal

Prof Erick Carvajal, received his Bachelors in Electrical Engineering at Universidad de Costa Rica in 2014, his Masters of Science in Electrical Engineering at The University of Texas at Austin in 2017 and his PhD in Computer Engineering from Texas A&M University in 2021, where his research was co-advised by Dr. Jiang Hu and Dr. Paul Gratz. His interests include the integration of Machine Learning techniques into the IC design flow to make designs faster and more efficiently, as well as the application of innovative techniques for teaching engineering classes.