OpenROAD™ is a foundational application for open-source VLSI design from RTL to GDSII. It is used widely by many popular Open Source tools and initiatives that foster and enable ASIC and FPGA design flows and methodologies. One such initiative is FASoC, a DARPA-funded program across multiple universities and industry leaders such as Arm, led by the University of Michigan.

Automating Analog Design using OpenROAD

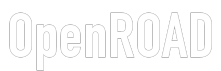

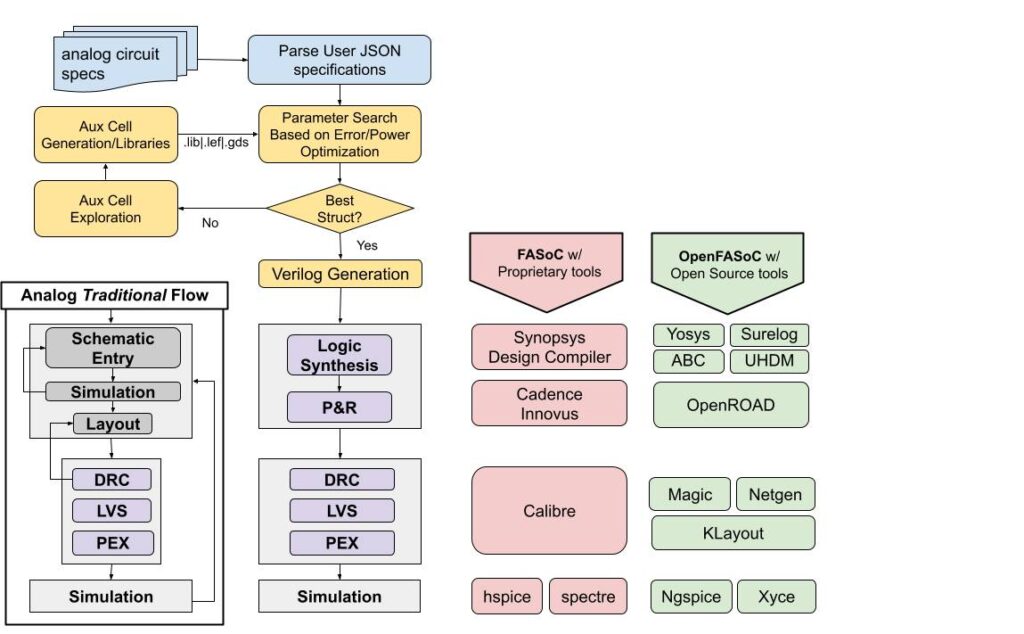

FASoC consists of a set of tools and scripts, mainly based on python and Tcl used to implement a single pass, RTL-GDSII flow. OpenFASoC uses the OpenROAD application to generate GDS from verilog for both analog and digital components. Conventional analog designs require schematic-entry based specification and a custom layout design that requires many iterations to meet design goals.

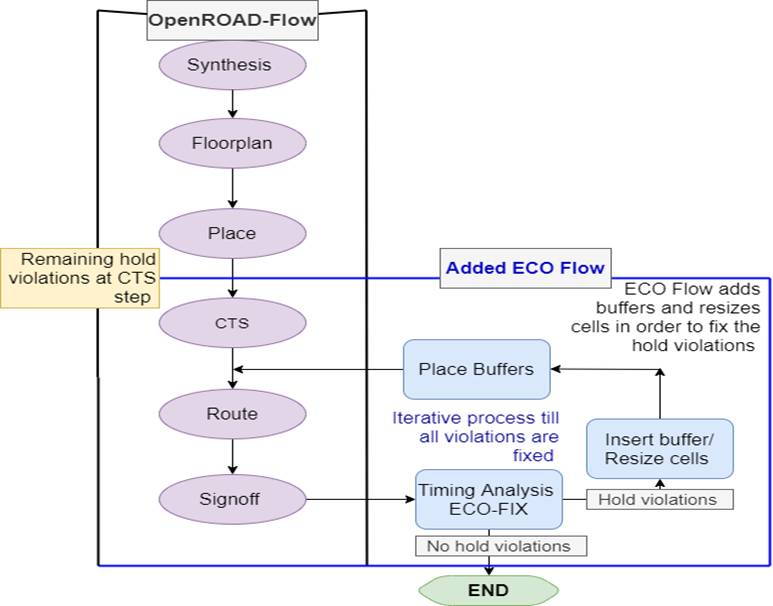

The automated OpenFASoC/OpenROAD-based flow shown below enables the integration of cell-based analog blocks into an SoC digital flow, thereby greatly increasing productivity by digitizing the analog design creation and implementation and enabling ease of integration into the SoC.

The OpenROAD™ API is flexible and allows fine control during physical design through the use of both Tcl and python based scripts to define floorplanning and power components. Complex physical design features like building macro functions to do symmetrical placements or arrays, guardbanding, etc. are easier in the OpenROAD flow as compared to proprietary tools.

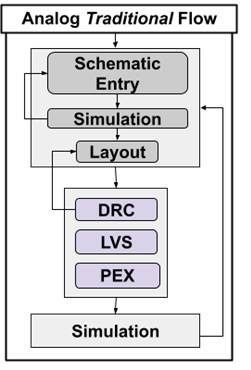

OpenFASoC on

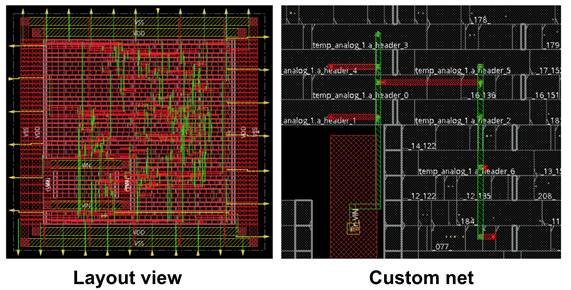

Figure shows a D-LDO generator design submitted in the Google MPW-II shuttle. It represents highly trimmable voltage references to address dependencies on or sensitivities to temperature variation. Switches and voltage reference structures are tightly placed using an evenly distributed placement to minimize variations.

The power stripes for the switches array are created to minimize resistivity.

OpenTitan FASoC with OpenROAD ECO flow

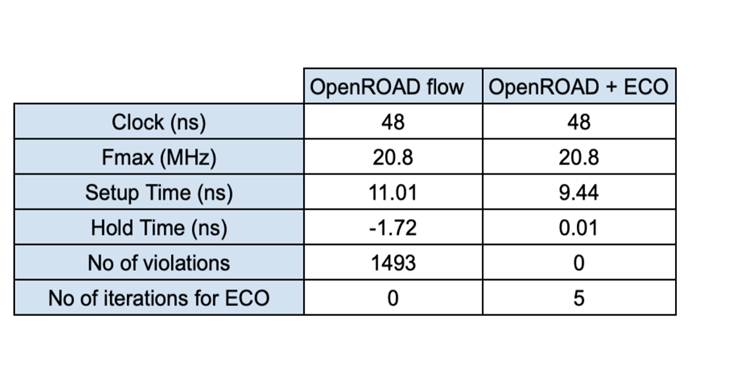

OpenROAD™ supports a modular ECO flow to augment timing optimization and closure through iterative buffer sizing and insertion on timing critical paths. The ECO flow is important and necessary, especially in low power designs which are tightly constrained to optimize power for a target speed. The table above shows that hold violations were fixed at target clock of 20MHz in five iterations.

OpenFASoC also uses custom functions to control placement, power stripe generation and

custom routing for good PPA. Future work involves support for multiple voltage domains.

Reference Links

https://github.com/idea-fasoc/OpenFASOC

https://github.com/msaligane/caravan_openfasoc