2022 has been a very exciting and productive year for the OpenROAD™ project. We made good progress across main project areas including core technologies, tool quality, PPA outcomes and targeted outreach programs. This has led to a wider usage of our tools in various applications and an exponential growth in our user community.

Our core mission is to make OpenROAD based IC design easy-to-use, learn-at-scale and foster system level innovation.Here are some of the key project achievements of 2022 towards these goals.

Key Innovations in Core Technologies, Cloud and ML based execution

We added several new tools and enhanced core tool functionality in the database, partitioning, placement, floorplanning and routing tools to significantly improve runtime, design quality and flow robustness.

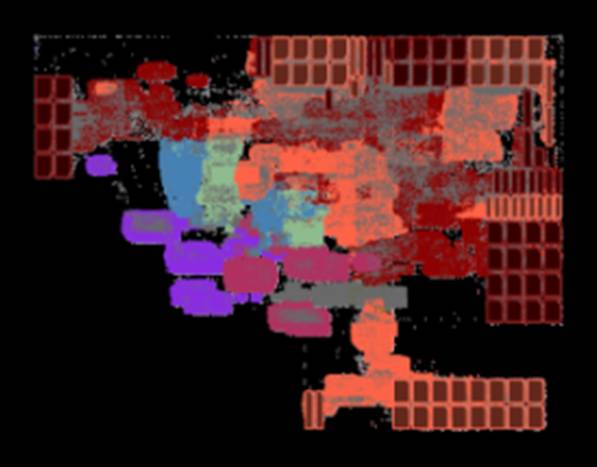

A Hierarchy-aware Macro placer

RTL-MP was created to give RTL designers more control and early insights into physical implementation, make architectural tradeoffs through intelligent logic-aware choices, smart clustering and shaping clouds of logic native to the logical hierarchy. This results in dense layouts with superior performance, utilization and area comparable to custom design.

Figure below is a sample design that shows an RTL-MP generated layout for a 12nm Black Parrot design. Macro placements were automatically deduced with knowledge of placement constraints to improve performance (fmax) and reduce wire lengths to achieve quality which is comparable to custom layout quality.

Rapid Design Exploration and PPA Estimation using ML – AutoTuner

As part of our ongoing research to continually improve PPA without increasing runtime, we created the OpenROAD™ AutoTuner to enable designers to rapidly explore the design space for a range of design configurations by leveraging the power of machine learning and cloud computing. AutoTuner’s hyperparameter optimization allows designers to automatically set up and execute thousands of experiments on the cloud thereby achieving PPA possible at a fraction of the cost and runtime.

AutoTuner test results on representative benchmarks (like IBEX on sky130) reveal up to a 3X improvement in runtime. These were tested using a Kubernetes Ray cluster over GCP with a provision for distributed detailed routing with one load balancer and 30 servers of 15 CPUs. Detailed testing on the router provided clear insights into architectural tradeoffs of distributed vs multi-threaded processing, single vs multiple machine configurations.

Leveraging the Cloud for Efficient Resources and Performance

OpenROAD’s COPILOT: Cloud Optimized Physical Implementation Leveraging OpenROAD Technology, intelligently deploys cloud and compute resources to enhance runtime performance of the distributed router. Our research yielded intelligent interventions in predicting failed runs and focusing on stubborn, recurring subproblems such as DRC failures allowing better control of batch executions. Early testing shows a 10X speedup in detailed routing in select test cases before reaching a plateau.

A new partitioner (TritonPart) aims to better manage design instance constraints and cluster engines to yield good global placement which is key to achieving good design quality and faster closure with a potential for a 1X speedup.

In 2022, OpenROAD added support for a tighter integration of design data to its open database (ODB) that significantly improved incremental design analyses and optimization. We began creating a full python API to OpenROAD to make it easier to extend and utilize python ML based libraries in applications;this further improved runtime performance especially during optimization.

A hierarchical design methodology vastly simplifies design complexity, memory usage and runtime management for large designs (>500k instances). The timing model from netlist was enhanced to provide better support for design hierarchy and include extracted parasitics at block and interconnect signals for accurate top-level timing analysis.

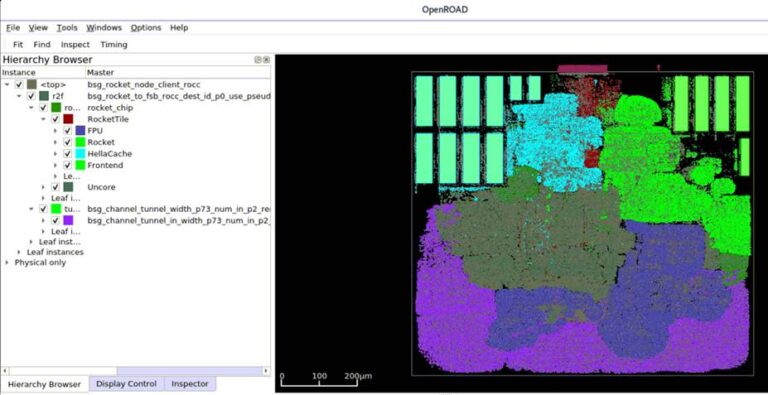

The OpenROAD GUI was significantly enhanced– It supports better hierarchy browsing, viewing and analyzing problems such as off-grid pins and routing, rulers and markers, and heatmaps for hotspot analyses.

Improved QoR through Continuous Innovation and CI

In 2022 we sharpened our focus on PPA targets. The AutoTuner allows designers to get over a 3X runtime speedup over manual design, with best achievable PPA based on user constraint ranges for design parameters. Furthermore, users can capture key design metrics and continuously track QoR and interventions to improve them.

RTL-MP showed great potential for large designs in enabling RTL designers to make early design tradeoffs with rapid feedback from the floorpan and thus get better QoR without sacrificing speed.

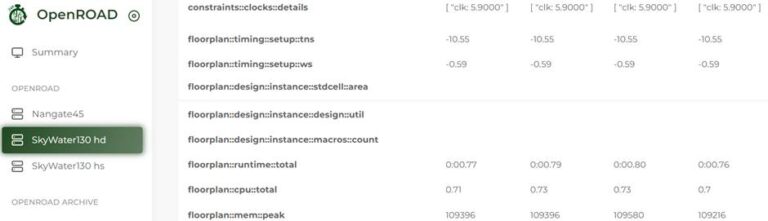

We saw QoR improvements throughout our gallery of designs. Here is a sample public dashboard that captures and tracks QoR changes across our nightly builds across a gallery of designs: https://dashboard.theopenroadproject.org/. Design metrics are captured for nightly builds and compared against golden runs for goodness.

We plan to make such capabilities available to users to enable them to capture key design metrics and track QoR across design changes.

OpenROAD™ continued its synergy with the MacroPlacement effort to provide an open, transparent version of Google Brain’s deep reinforcement learning-based method.

Silicon Support and Tapeouts

We had several notable design successes: intel16 tapeout by Army Labs (ARL) and a GF12 based mixed-signal design by the University of Michigan. The ARL tapeout also advanced capabilities in the power network creation along with automatic I/O Pad placement functionality.

We also prioritized PDK support as a key enabler of open-source design; we added support for GF180MCU public PDK that launched the first Google sponsored shuttle on this node.

As part of the ongoing effort to improve tool quality and results, we implemented a continuous and automated CI for over 100 Open MPW user designs from shuttles MPW2-7. This helps find QoR degradations, tool bugs and other flow issues. Using GitActions based workflows, users can automatically monitor and update their designs based on QoR or software update alerts from their CI. OpenLane was used in > 600 tapeouts to-date from MPW5-7 onwards to MPW-8.

Enhancing Industry focus, User communications and Outreach

We made a lot of progress in our communication and outreach programs to expand our community for an improved learning experience and productive engagement. A new website now shares important updates and provides access to key resources such as tutorials, papers, blogs and interesting user stories showcasing interesting use models and innovations in research: https://theopenroadproject.org/user-stories/. As a result, we have seen a rapid increase in user subscription through our website and GitHub.

OpenROAD is fast becoming the de facto application for Open-Sourced IC design tools for research and skill development. OpenROAD is an ongoing training partner for IC design courses with UCSC extension– two courses as part of UCSC extension in the fall of 2022 : Advanced Physical Design and Timing closure. https://www.ucsc-extension.edu/certificates/vlsi-engineering/. These courses continue in 2023.

Several Universities have signed MoUs to use OpenROAD based design courses. University of Costa Rica, taught a semester-long course on Microelectronics and basic VLSI design. OpenROAD continues to drive global research, innovation and workforce development at major universities and the general body of users.

We offered three OpenROAD based internship projects at GSoC 2022 with a goal of fostering direct contribution in the form of tutorials, documentation and other development needs. This is a great opportunity for students to learn, contribute and advance their skills in EDA tools and IC design.

Tom Feist joined us as part of the EEI – Embedded Entrepreneur Initiative to guide the project along a path towards Industry adoption and product stabilization.

OpenROAD Focus for 2023

The following are key areas of focus planned for 2023:

- Enhance usability in software installation, distribution and execution. Runtime efficiency through effective partitioning, distribution and multi-threaded processing over a single machine and across the cloud.

- Major features support:

- OpenROAD as a cockpit for fast, low-cost design exploration and prediction for high-confidence convergence and handoff to back-end implementation in OpenROAD and other EDA tools.

- Support for UPF, dynamic power simulation, multiple-power domains

- A hierarchical macro placer that is more efficient for hierarchical placements. This will replace the default macro placer.

- Basic support for DFT- scan-chain integration

- CTS improvements

- Enhanced timing model for better accuracy

- Enhanced support for public and private PDKS for design exploration at key technology nodes

- Skywater (SKY90) enablement

- Creation of proxy PDKs such as ASAP7 for accurate predictability for implementation in real applications

- QoR improvements – “Measure and track what you need to improve”

- Closing the gap to measurable PPA targets for important designs.These includes auto-tuning of key tools in the flow (router, cts etc.)

- Use important metrics through dynamic tracking and actionable insights both internally and to enable users to track their design progress in an ongoing manner.

- Education and Workforce Development

OpenROAD will expand initiatives through key partners to support and foster barrier-free, low/no-cost education for students, researchers and other professionals looking to upskill and gain employment in the semiconductor industry.

Finally, we would like to see you use OpenROAD™ in many more exciting applications and share your experiences with us! Reach out and share your ideas and comments : https://theopenroadproject.org/contact-us/

Stay tuned and Happy Learning in 2023 and onwards!